在當今數字化時代,一個高效的電子詞典應用不僅需要具備強大的本地詞庫,更應依托網絡技術提供即時、準確的翻譯與釋義服務。本項目旨在設計并實現一個基于客戶端-服務器(Client-Server)架構的電子詞典系統。通過清晰的網絡編程分工,客戶端負責用戶交互,服務器端負責數據處理與核心服務,兩者協同工作,為用戶提供流暢的查詢體驗。

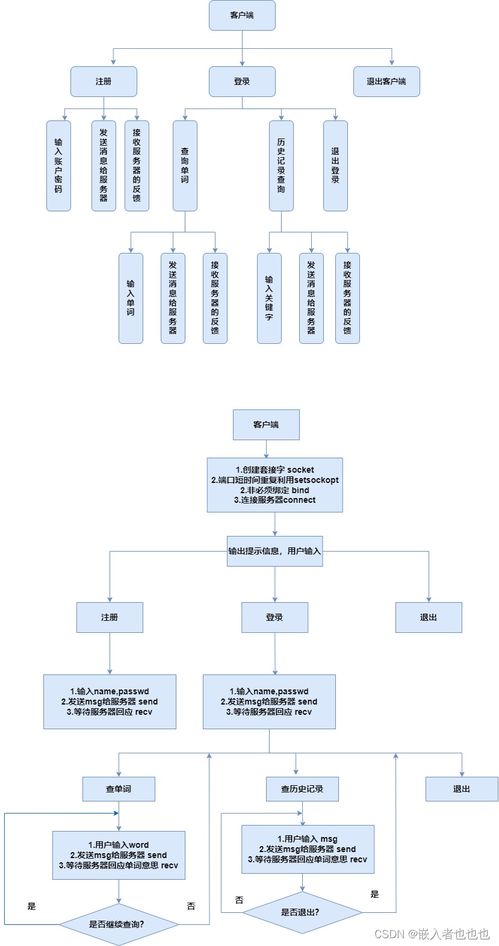

一、 核心功能需求圖

本項目的核心功能圍繞用戶查詢、系統響應和數據管理展開,形成以下需求結構:

- 用戶認證模塊:

- 用戶注冊與登錄:客戶端發送用戶名和密碼至服務器驗證。

- 會話管理:服務器維護登錄狀態,確保請求的合法性與安全性。

- 詞典查詢模塊(核心功能):

- 單詞/短語查詢:客戶端將用戶輸入的查詢詞(支持中英文)發送至服務器。

- 結果返回與展示:服務器查詢本地或在線數據庫,將詳盡的釋義、例句、音標及發音鏈接返回給客戶端進行格式化顯示。

- 查詢歷史記錄:服務器記錄用戶的查詢歷史,客戶端提供歷史查看與清空功能。

- 詞庫與數據管理模塊:

- 詞庫更新:服務器端可定期從權威數據源更新或擴展詞庫。

- 用戶生詞本:用戶可將查詢過的單詞加入個人生詞本,服務器進行存儲,客戶端支持生詞本的增刪改查及復習提醒。

- 輔助與系統功能:

- 網絡狀態檢測:客戶端實時監測與服務器的連接狀態。

- 設置與個性化:客戶端提供界面主題、查詢偏好等設置選項。

二、 系統架構與網絡編程角色

系統采用典型的C/S架構,利用TCP/IP協議確保可靠的數據傳輸。

- 服務器端:

- 角色:作為系統的“大腦”和數據中心。采用多線程或I/O多路復用技術(如

select/poll/epoll或異步框架),并發處理多個客戶端的連接請求,避免阻塞。

- 職責:

- 監聽指定端口,等待客戶端連接。

- 接收客戶端請求,解析協議(如自定義的簡單文本協議或JSON)。

- 處理業務邏輯:驗證用戶、查詢數據庫、記錄歷史、管理生詞本。

- 組織響應數據,并將其發送回對應的客戶端。

- 維護數據庫連接池,高效訪問詞庫數據(可使用SQLite、MySQL等)。

- 客戶端:

- 角色:作為系統的“面孔”和交互窗口。提供圖形用戶界面(GUI,如使用PyQt、Tkinter、Java Swing或跨平臺框架)或命令行界面。

- 職責:

- 建立與服務器的網絡連接(指定服務器IP和端口)。

- 接收用戶輸入,并封裝成符合協議的請求消息。

- 向服務器發送請求,并等待響應。

- 接收服務器響應,解析數據并在界面上友好地展示給用戶。

- 管理本地緩存(如最近查詢結果)以提升體驗。

三、 核心業務流程設計流程圖

以下以一次成功的單詞查詢為例,描述客戶端與服務器的交互流程:

開始

│

▼

[客戶端啟動,建立與服務器的TCP連接]

│

▼

[用戶輸入查詢單詞并點擊“查詢”]

│

▼

[客戶端封裝請求:{“action”: “query”, “word”: “hello”, “token”: “用戶會話令牌”}]

│

▼

[客戶端通過Socket發送請求數據流]

│

▼

[服務器端監聽線程接收連接/數據]

│

▼

[服務器工作線程解析請求,驗證令牌有效性] ──無效──> [返回錯誤信息]

│ 有效

▼

[服務器查詢核心詞庫數據庫]

│

▼

[找到記錄] ──未找到──> [可選:調用第三方在線詞典API補充]

│

▼

[服務器組織響應:{“status”: “success”, “data”: {釋義,例句...}}]

│

▼

[服務器通過同一Socket連接發送響應數據流]

│

▼

[客戶端接收響應數據流]

│

▼

[客戶端解析響應] ──失敗/錯誤──> [界面提示“查詢失敗”或“網絡錯誤”]

│ 成功

▼

[客戶端GUI更新,美觀地展示單詞釋義、例句等信息]

│

▼

[(可選)客戶端提示用戶是否將單詞加入生詞本]

│

▼

結束(連接可保持用于后續請求,或超時后關閉)四、 關鍵網絡技術服務與考量

- 通信協議設計:應用層需設計簡單、高效的消息協議(如每行一個字段的文本協議或輕量級的JSON),用于封裝動作、數據和狀態。

- 數據序列化:采用JSON或Protobuf等格式進行數據的序列化與反序列化,確保跨平臺兼容性和傳輸效率。

- 并發處理:服務器必須能夠處理高并發請求,使用線程池、異步I/O或事件驅動模型是關鍵。

- 錯誤處理與超時:網絡環境不穩定,客戶端和服務器都需要設置合理的讀寫超時,并進行異常捕獲,給出友好提示。

- 安全考慮:用戶密碼應加密傳輸(如使用哈希處理),防止中間人攻擊;對請求頻率可做適當限制。

###

通過將電子詞典項目分解為客戶端與服務器兩大模塊,并配以明確的功能需求圖和交互流程圖,我們構建了一個清晰、可擴展的網絡應用藍圖。客戶端專注于提供直觀易用的界面,服務器則專注于提供穩定、高效的數據服務。利用成熟的網絡編程技術(Socket編程、多線程/異步處理、數據庫訪問)和合理的數據協議,可以成功搭建一個功能完整、響應迅速的現代化電子詞典服務系統。